DFT技術(shù)在集成電路設(shè)計(jì)中的關(guān)鍵作用與應(yīng)用

隨著集成電路規(guī)模的不斷擴(kuò)大和復(fù)雜度的持續(xù)提升,設(shè)計(jì)驗(yàn)證與測試已成為芯片開發(fā)流程中至關(guān)重要的環(huán)節(jié)。可測試性設(shè)計(jì)(Design for Testability,簡稱DFT)技術(shù)應(yīng)運(yùn)而生,成為現(xiàn)代集成電路設(shè)計(jì)中不可或缺的重要組成部分。

一、DFT技術(shù)的基本概念與重要性

DFT是指在芯片設(shè)計(jì)階段就考慮測試需求,通過插入特定的測試結(jié)構(gòu)來提高芯片可測試性的設(shè)計(jì)方法。其主要目標(biāo)包括:

- 提高故障覆蓋率

- 降低測試成本

- 縮短測試時間

- 簡化測試程序開發(fā)

在納米級工藝時代,芯片內(nèi)部結(jié)構(gòu)日益復(fù)雜,傳統(tǒng)的功能測試方法已無法滿足測試需求。DFT技術(shù)通過在設(shè)計(jì)中添加專門用于測試的邏輯,使得芯片在制造完成后能夠被有效、全面地測試。

二、主要DFT技術(shù)方法

1. 掃描鏈設(shè)計(jì)(Scan Design)

掃描鏈?zhǔn)亲罨A(chǔ)且應(yīng)用最廣泛的DFT技術(shù)。通過將時序元件(如觸發(fā)器)改造成可串行移位的工作模式,形成掃描鏈結(jié)構(gòu),實(shí)現(xiàn)對內(nèi)部節(jié)點(diǎn)的控制和觀察。

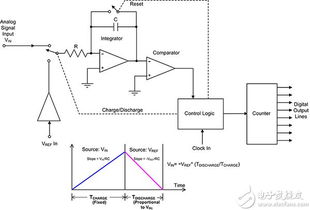

2. 內(nèi)建自測試(BIST)

BIST技術(shù)在芯片內(nèi)部集成測試向量生成器和響應(yīng)分析器,使芯片能夠自主完成測試。主要包括邏輯BIST和存儲器BIST兩大類。

3. 邊界掃描(Boundary Scan)

遵循IEEE 1149.1標(biāo)準(zhǔn),主要用于測試芯片間互連和板級連接,特別適用于系統(tǒng)級測試和多芯片模塊測試。

4. 測試壓縮技術(shù)

通過嵌入式壓縮解壓縮結(jié)構(gòu),顯著減少測試數(shù)據(jù)量和測試應(yīng)用時間,同時保持高故障覆蓋率。

三、DFT設(shè)計(jì)流程與實(shí)施要點(diǎn)

現(xiàn)代DFT設(shè)計(jì)通常遵循以下流程:

- 測試需求分析與規(guī)劃

- DFT架構(gòu)設(shè)計(jì)

- 測試邏輯插入

- 測試向量生成

- 故障仿真與覆蓋率分析

- 測試程序開發(fā)

實(shí)施DFT時需重點(diǎn)考慮:

- 面積開銷控制

- 時序影響分析

- 功耗管理

- 測試時間優(yōu)化

四、DFT技術(shù)的發(fā)展趨勢

隨著人工智能、5G、物聯(lián)網(wǎng)等新興應(yīng)用的快速發(fā)展,DFT技術(shù)也在不斷創(chuàng)新:

- 面向特定領(lǐng)域的DFT解決方案

- 基于機(jī)器學(xué)習(xí)的智能測試優(yōu)化

- 三維集成電路的測試挑戰(zhàn)與解決方案

- 安全性測試與硬件木馬檢測

五、結(jié)語

DFT技術(shù)作為集成電路設(shè)計(jì)的重要支撐,已經(jīng)從可選技術(shù)發(fā)展成為必需技術(shù)。優(yōu)秀的DFT設(shè)計(jì)不僅能確保芯片質(zhì)量,還能顯著降低測試成本,提高產(chǎn)品競爭力。隨著芯片復(fù)雜度的持續(xù)提升,DFT技術(shù)將繼續(xù)演進(jìn),為半導(dǎo)體產(chǎn)業(yè)的發(fā)展提供堅(jiān)實(shí)保障。

如若轉(zhuǎn)載,請注明出處:http://m.qdbailida.cn/product/19.html

更新時間:2026-02-20 17:36:58